IP Core: GECKO3COM simple

This is the documentation about the GECKO3COM simple IP core which is meant to be used in FPGA designs without an embedded processor. If you plan to build a microblaze based FPGA design use the GECKO3COM plb IP core.

This is the documentation about the GECKO3COM simple IP core which is meant to be used in FPGA designs without an embedded processor. If you plan to build a microblaze based FPGA design use the GECKO3COM plb IP core.

Usage

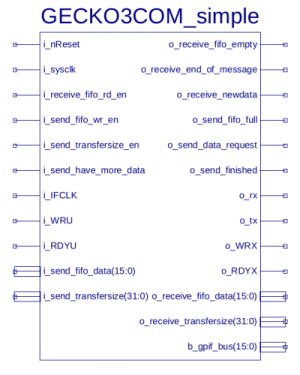

Port description

| Generic name | Type | Default Value | Description |

|---|---|---|---|

| BUSWIDTH | integer | 32 | Vector size of the FIFO databuses |

| Port name | Direction | Type | Description |

|---|---|---|---|

| i_nReset | in | std_logic | Low-active, asynchronous reset |

| i_sysclk | in | std_logic | FPGA System Clock |

| i_receive_fifo_rd_en | in | std_logic | Receive FIFO read enable signal. o_receive_fifo_data will we valid one clock cycle after the read enable is activated |

| o_receive_fifo_empty | out | std_logic | Receive FIFO empty signal |

| o_receive_fifo_data | out | std_logic_vector(BUSWIDTH-1 downto 0) | Receive FIFO data |

| o_receive_transfersize | out | std_logic_vector(31 downto 0) | Transfer length read from the TMC header. The host will write this number of bytes to the device |

| o_receive_end_of_message | out | std_logic | All data expected to be received is available in the receive FIFO |

| o_receive_newdata | out | std_logic | A new valid OUT transfer header was detected. The o_receive_transfersize value is valid and new data will be available in the receive FIFO |

| i_send_fifo_wr_en | in | std_logic | Send FIFO write enable signal. The FIFO will store the data on the next rising edge of i_sysclk |

| o_send_fifo_full | out | std_logic | Send FIFO full signal |

| i_send_fifo_data | in | std_logic_vector(BUSWIDTH-1 downto 0) | Send FIFO data |

| i_send_transfersize | in | std_logic_vector(31 downto 0) | Number of bytes of the response data to be sent to the host. It must be lower or equal o_receive_transfersize |

| i_send_transfersize_en | in | std_logic | Send transfer size write enable signal. The i_send_transfersize value will be stored on the next rising edge of i_sysclk. This also signals to the IP core that data is ready to be sent to the host |

| i_send_have_more_data | in | std_logic | Set this signal if there is more data to be sent to the host than the maximum number of bytes requested by the host (Response data length greater than o_receive_transfersize) |

| o_send_data_request | out | std_logic | The host has requested data from the device. The o_receive_transfersize value is valid (This is the maximum allowed number of bytes to be sent). The core is waiting for data in the send FIFO and that a valid value is written to i_send_transfersize |

| o_send_finished | out | std_logic | Signals that the core is finished sending data to the host |

| o_rx | out | std_logic | Receiving data signalization |

| o_tx | out | std_logic | Transmitting data signalization |

| Interface signals to the EZ-USB FX2 | |||

| i_IFCLK | in | std_logic | GPIF CLK (GPIF is Master and provides the clock) |

| i_WRU | in | std_logic | Write request from GPIF |

| i_RDYU | in | std_logic | GPIF is ready |

| o_WRX | out | std_logic | Request to write to the GPIF |

| o_RDYX | out | std_logic | FPGA is ready |

| b_gpif_bus | inout | std_logic_vector(SIZE_DBUS_GPIF-1 downto 0) | Bidirectional data bus |

Logic utilization

This numbers show the logic utilization of the whole GECKO3COM_simple_test project which includes a bit more logic elements than the GECKO3COM simple IP core alone.

| Resource Type | Used | Available (Spartan3 4000) | Utilization |

|---|---|---|---|

| Number of Slice Flip Flops | 909 | 55,296 | 1% |

| Number of occupied Slices | 804 | 27,648 | 2% |

| Total Number of 4 input LUTs | 1,137 | 55,296 | 2% |

| Number of bonded IOBs | 30 | 489 | 6% |

| Number of RAMB16s | 4 | 96 | 4% |

| Number of BUFGMUXs | 2 | 8 | 25% |