Memory components

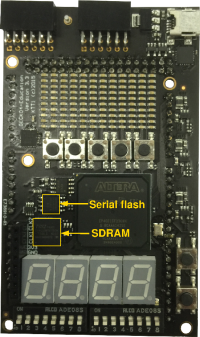

The GECKO4-Education platform contains a SDRAM and serial flash memory as indicated in the below figure.

SDRAM information

The GECKO4-Education contains a 32MByte mobile synchronous DRAM (M-SDRAM). The datasheets can be found here.

This SDRAM can be used with the external SDRAM memory controller of QSYS. The below tables indicate the FPGA-pins to which the SDRAM is connected. And here you find an example tcl script that can be used for pin-assignment in Quartus.

Address bus:

| Address bit: | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| FPGA-pin: | PIN_V2 | PIN_U8 | PIN_U2 | PIN_V4 | PIN_V1 | PIN_V5 | PIN_V6 | PIN_V7 | PIN_W6 | PIN_P5 | PIN_P4 | PIN_N6 | PIN_N5 |

Data bus:

| Data bit: | 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| FPGA-pin: | PIN_AA4 | PIN_AB3 | PIN_AA1 | PIN_Y3 | PIN_Y2 | PIN_Y1 | PIN_W2 | PIN_W1 | PIN_P3 | PIN_P2 | PIN_P1 | PIN_N2 | PIN_N1 | PIN_M3 | PIN_M2 | PIN_M1 |

Control signals:

| Function: | short: | FPGA-pin: |

|---|---|---|

| Bank Select high | BA[1] | PIN_M7 |

| Bank Select low | BA[0] | PIN_M6 |

| Byte Select high | DQM[1] | PIN_V3 |

| Byte Select low | DQM[0] | PIN_R1 |

| Clock enable | CKE | PIN_U7 |

| Clock | CLK | PIN_AA3 |

| Colum address select (active low) | nCAS | PIN_M5 |

| Row address select (active low) | nRAS | PIN_M4 |

| Chip select (active low) | nCS | PIN_U1 |

| Write enable (active low) | nWE | PIN_R2 |

Flash information

The GECKO4-Education board contains besides the FPGA-configuration FLASH also a 8MByte serial FLASH memory. The datasheets of this component is available here.

The below table shows the FPGA-pin connections. And here you find an example tcl script that can be used for pin-assignment in Quartus.

| Function: | short: | FPGA-pin: |

|---|---|---|

| Chip select (active low) | NCS | PIN_U14 |

| Hold (active low) or IO3 | NHOLD_IO3 | PIN_U13 |

| Serial clock | SCK | PIN_V13 |

| Serial in or IO0 | SI_IO0 | PIN_W13 |

| Serial out or IO1 | SO_IO0 | PIN_V14 |

| Write protect (active low) or IO2 | NWP_IO2 | PIN_W14 |